|

Опросы |

|

Консультации |

|

| Сигналы спутниковых радионавигационных систем |

|

| Отечественные и зарубежные бортовые РЛС |

|

| Бортовая РЛС "Копье-21" |

|

| Системы селекции движущихся целей |

|

| РЛС с синтезированием апертуры антенны |

|

|

Информация |

|

| О тестировании |

|

Микропроцессоры семейства TMS320C8X

Микропроцессор TMS320C80, выпущенный в конце 1994 года, имеет второе название - MVP (Multimedia Video Processor - мультимедийный видеопроцессор), что обусловлено его высокой эффективностью на задачах обработки изображений, в системах виртуальной реальности, компрессии и декомпрессии видео- и аудиоданных, обработки связной информации.

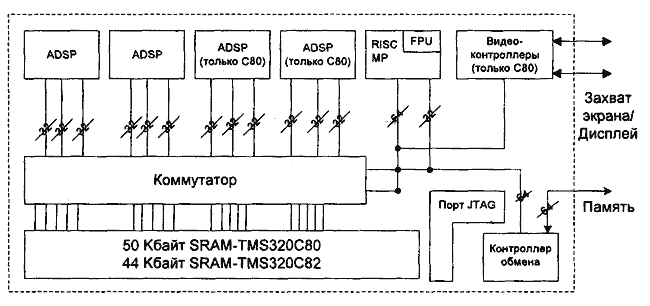

TMS320C80 представляет собой новый подход к повышению производительности и функциональности цифровых сигнальных процессоров: в одной микросхеме объединено четыре усовершенствованных цифровых процессора обработки сигналов (ADSP - Advanced Digital Signal Processor), каждый из которых выполняет за такт несколько RISC-операций, и пятый процессор, называемый главным процессором (Master Processor - МР), - 32-разрядный процессор с высокопроизводительным устройством обработки чисел в формате с плавающей точкой. В дополнение к процессорному ядру на кристалле размещены:

- контролер обмена (ТС - Transfer Controller) - интеллектуальный контроллер ПДП, поддерживающий интерфейс с DRAM и SRAM;

- видеоконтроллер (VC - Video Controller);

- порт тестирования и отладки - JTAG;

- 50 Кбайт SRAM.

Выпускается также упрощенный вариант микропроцессора TMS320C82, который отличается меньшим объемом памяти, количеством сигнальных процессоров ADSP (2), отсутствием видеоконтроллера и, соответственно, меньшей стоимостью.

Структура процессора изображена на рис. 9.

Рис. 9. Структура микропроцессора TMS320C8X

Суммарная производительность TMS320C80 на регистровых операциях достигает 2 млрд RISC-подобных команд в секунду. Благодаря столь высокой производительности TMS320C80 может заменить при реализации ряда приложений более 10 высокопроизводительных сигнальных микропроцессоров или универсальных микропроцессоров, выпускавшихся до его появления.

Приведем технические характеристики TMS320C80:

- тактовая частота 40 или 50 МГц;

- производительность свыше 2 млрд операций в секунду;

- 64-разрядный контроллер обмена с динамическим конфигурированием шины на обмен 64-, 32-, 16- и 8-разрядными словами;

- режим ПДП к SRAM, DRAM;

- пропускная способность шины памяти - 2,4 Гбайт/с при передаче данных и 1,8 Гбайт/с при передаче команд;

- объем адресного пространства - 4 Гбайт;

- поддержка до 4 внешних прерываний; П напряжение питания 3,3 В;

- около 4 млн транзисторов на кристалле;

- технология производства КМОП 0,5 мкм.

Архитектура микропроцессора TMS320C80

Архитектура процессора TMS320C80 относится к классу MIMD - множественный поток данных, множественный поток команд. Входящие в состав TMS320C80 процессоры программируются независимо один от другого и могут выполнять как разные, так и одну общую задачу. Обмен данными между процессорами осуществляется через общую внутрикристальную память, доступ к которой обеспечивает матричный коммутатор (Crossbar), выполняющий также функции монитора при одновременном обращении к одному сегменту памяти нескольких процессоров.

Рассмотрим подробнее архитектуру процессоров, входящих в состав TMS320C80.

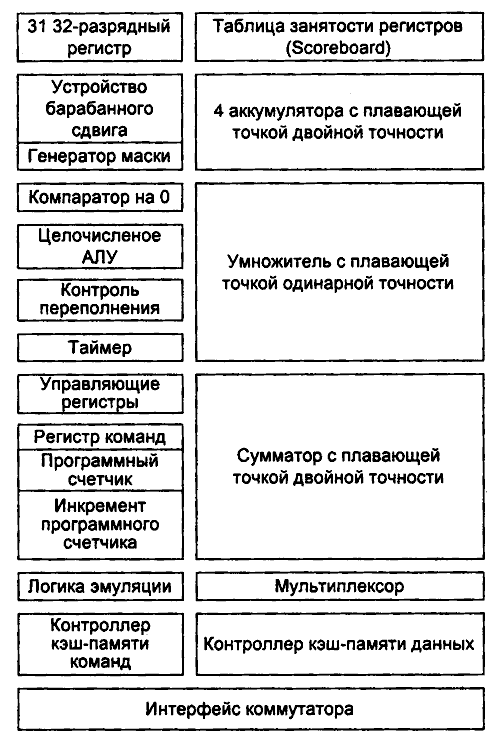

Архитектура главного процессора

Главный процессор - это вычислительное устройство с RISC-архитектурой и встроенным сопроцессором для выполнения операций с плавающей точкой. Подобно другим процессорам с RISC-архитектурой, МР использует команды загрузки/сохранения для доступа к данным в памяти, а также выполняет большинство целочисленных, битовых и логических команд над операндами в регистрах в течение одного такта.

Вычислитель с плавающей точкой (FPU - Floating Point Unit) конвейеризирован и позволяет выполнять операции над данными как с одинарной, так и с двойной точностью, совмещая в конвейере операции умножения, сложения с накоплением, загрузки и сохранения результата. FPU использует тот же регистровый файл, что и устройство целочисленной и логической обработки. Производительность устройства составляет около 100 Mflops. Специальный механизм отметок (Scoreboard) фиксирует занятость регистров и обеспечивает их бесконфликтное использование.

На рис. 10 приведена структура главного процессора.

Рис. 10. Структура главного процессора

Основными компонентами МР являются:

- регистровый файл, состоящий из 31 регистра (32-разрядного);

- барабанное устройство сдвига (Barrel Rotator);

- генератор маски;

- таймер;

- целочисленное АЛУ;

- управляющий регистр;

- 4 аккумулятора с плавающей точкой двойной точности;

- умножитель с плавающей точкой;

- сумматор с плавающей точкой;

- контролер кэш-памяти.

Объем каждого из внутрикристальных кэшей МР для команд и данных равен 4 Кбайта. Управление кэш-памятью осуществляет входящий в состав МР контроллер.

МР может обслуживать до четырех внешних прерываний. Запрос на обслуживание трех из них должен иметь форму импульса, а для одного - передача управления процедуре обработки осуществляется по изменению уровня напряжения.

Для различных схем распараллеливания обработки в рамках микропроцессора МР может использоваться как управляющий или как универсальный арифметико-логический и графический процессор.

Набор инструкций МР включает в себя:

- арифметические операции;

- логические операции;

- операции сравнения;

- операции с плавающей точкой;

- арифметические преобразования;

- векторные арифметические операции;

- векторные операции умножения/накопления;

- векторные операции преобразования;

- векторные операции умножения/накопления с удвоенной точностью;

- операции ветвления и переключения контекста;

- команды управления;

- команды чтения/записи ОЗУ;

- команды сдвига.

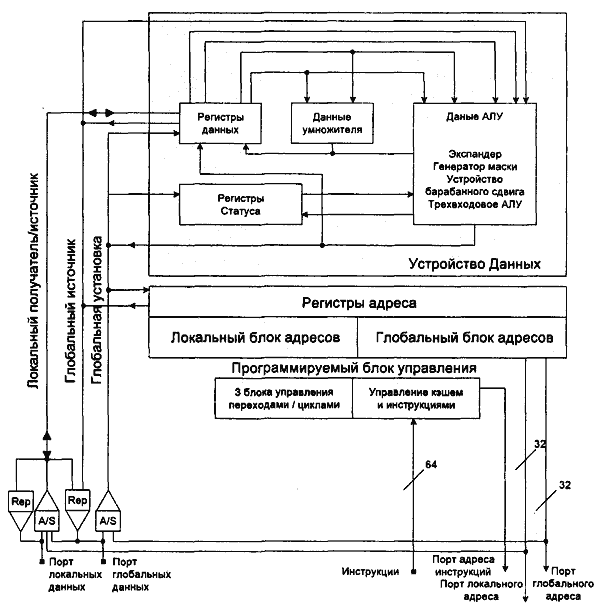

Архитектура ADSP-процессоров

Архитектура ADSP-процессоров TMS320C80 оптимизирована для приложений, связанных с обработкой 2- и 3-мерной графики, видеоизображений и звука. ADSP может выполнять за один такт одновременно операцию умножения, арифметико-логическую операцию (например, сдвиг-суммирование) и два обращения к памяти. Внутренний параллелизм ADSP позволяет обеспечить на некоторых алгоритмах быстродействие свыше 500 млн операций в секунду.

ADSP манипулирует 32-разрядными словами, а разрядность команд составляет 64 бита. Процессор использует прямую, непосредственную и 12 видов косвенной адресации.

Архитектура ADSP характеризуется следующими параметрами:

- 3-этапный конвейер;

- 44 доступных пользователю регистра (10 адресных, 6 индекса, 8 данных, 20 - прочих);

- 32-разрядное 3-входовое АЛУ; О репликатор битов;

- два адресных устройства;

- 32-разрядное устройство барабанного сдвига; О генератор масок;

- блок условных операций (для сокращения времени выполнения переходов).

Структура ADSP-процессора показана на рис. 11.

Рис. 11. Структура ADSP-процессора

На рисунке обозначены:

- A/S - блок выравнивания/расширения знакового разряда

- Repl - репликатор.

Контроллер обмена

Контроллер обмена управляет операциями обмена процессоров и памяти как внутри кристалла (через коммутатор), так и вне кристалла, с использованием входящих в его состав интерфейсных схем, поддерживающих все распространенные стандарты памяти (DRAM, VRAM, SRAM) и обеспечивающих возможность динамического изменения разрядности шины от 8 до 64. Используя приоритетную дисциплину обслуживания запросов к памяти в режиме ПДП, контроллер обмена позволяет выполнять обмен данными, не прерывая вычислений со скоростью до 400 Мбайт/с.

Контроллер обмена поддерживает линейную и координатную адресацию памяти для эффективного выполнения обмена при работе с 2- и 3-мерными графическими изображениями.

Видеоконтроллеры

Два расположенных на кристалле микропроцессора TMS320C80 видеоконтроллера обладают возможностью захвата и отображения видеоинформации в режимах как вертикального, так и горизонтального сканирования. Режимы захвата/сканирования могут устанавливаться для каждого из контроллеров независимо.

Области применения микропроцессора TMS320C80

Области применения микропроцессора гораздо шире тех, что обозначены его названием. Процессор нашел свое применение в системах: обработки мультимедийной информации, видеоконференцсвязи, обработки 2- и 3-мерной графики, моделирования виртуальной реальности, передачи данных.