|

Опросы |

|

Консультации |

|

| Сигналы спутниковых радионавигационных систем |

|

| Отечественные и зарубежные бортовые РЛС |

|

| Бортовая РЛС "Копье-21" |

|

| Системы селекции движущихся целей |

|

| РЛС с синтезированием апертуры антенны |

|

|

Информация |

|

| О тестировании |

|

Микропроцессоры семейства TMS320C6X

Новое семейство процессоров ЦОС компании Texas Instruments - TMS320C6x - включает в себя процессоры как с фиксированной, так и с плавающей точкой. Первый представитель данного семейства TMS320C6201 оперирует с данными только в формате с фиксированной точкой.

На тактовой частоте 200 МГц микропроцессор имеет производительность до 1,6 млрд операций в секунду. Областями его применения являются:

- беспроводные системы передачи данных;

- средства удаленной медицинской диагностики;

- базовые станции мобильной связи;

- модемные пулы и серверы удаленного доступа;

- xDSL и кабельные модемы;

- многоканальные телефонные платформы, офисные коммутаторы, системы речевой передачи сообщений;

- мультимедийные системы.

TMS320C6201 помимо процессорного ядра содержит:

- 1 Мбит внутрикристальной памяти (512 Кбит для программы, 512 Кбит для данных);

- 32-битный интерфейс внешней памяти, поддерживающий стандарты памяти SDRAM, SBSRAM, SRAM;

- два последовательных расширенных буферизированных порта;

- 16-битный порт центрального процессора;

- два канала доступа к памяти данных с возможностью начальной загрузки;

- генератор интервалов времени.

Построенный в соответствии с разработанной компанией Texas Instruments архитектурой VelociTI, процессор С62хх - первый из сигнальных VLIW-процессоров, использующий для повышения производительности параллелизм уровня команд.

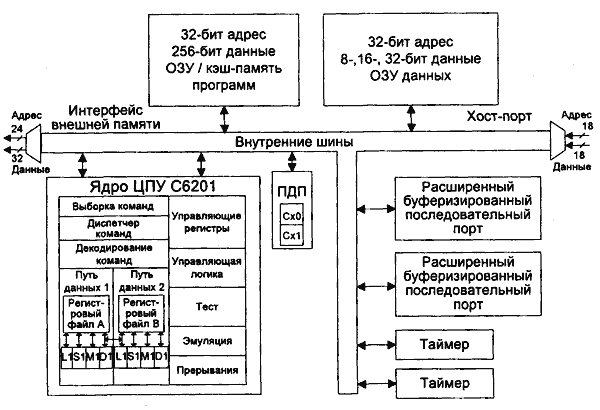

Структура микропроцессора TMS320C6201 приведена на рис. 12.

Рис. 12. Структура микропроцессора TMS320C6201

Процессор TMS320C6201 состоит из трех основных частей: центрального процессора (ядро), периферийных устройств и памяти.

Ядром TMS320C6201 является VelociTI VLIW-процессор с 8 функциональными модулями, включая 2 умножителя и 6 АЛУ. Модули взаимодействуют через два регистровых файла, содержащих по 16 32-разрядных регистров. ЦП может выполнять до 8 команд за один такт.

Программный параллелизм выявляется на этапе компиляции, анализ зависимости по данным аппаратными средствами на стадии выполнения не производится. Код выполняется на независимых функциональных устройствах в последовательности, задаваемой программой.

В процессоре используется упаковка команд, сокращающая размеры кода и время выборки команд. 256-разрядная шина памяти программ позволяет выбирать за один такт восемь 32-разрядных команд. Все команды содержат условия их выполнения, что позволяет сократить расходы производительности процессора на выполнение переходов и увеличить степень параллелизма обработки.

Процессор может оперировать с 8/16/32-разрядными данными. Для приложений, требующих высокой точности вычислений, предусмотрена возможность вычислений с 40-разрядными операндами. Для результатов всех основных арифметических операций выполняется округление и нормализация. В процессоре реализованы операции над битовыми полями, такие как "выделить" (extract), "установить" (set), "очистить" (clear), "подсчет битов" (bit counting).

Центральный процессор имеет два тракта обработки данных, каждый из которых содержит функциональные модули (L, S, M, D) и регистровый файл (16 32-разрядных регистров). Функциональные модули выполняют сдвиг, умножение, логические и адресные операции. Все операции выполняются над регистрами. Два набора устройств адресации данных (D1 и D2) отвечают исключительно за все пересылки данных между регистровым файлом и памятью. Управляющий регистровый файл определяет различные аспекты функционирования процессора.

Процесс обработки VLIW начинается с выборки из памяти команд 256-битного пакета. Команды связываются для совместного выполнения в выполняемый пакет (до 8 команд) по значению младшего бита команды.

Устройство выборки-декодирования-диспетчеризации команд может направлять к функциональным модулям до 8 команд (32-разрядных) за один такт по каждому из путей обработки (А и В).

В С62хх реализованы прямой и циклический (для регистров А4-А7 и В4-В7) способы адресации. Способ адресации определяется регистром режима адресации (AMR - Address Mode Register).

Процессоры семейства С62хх имеют 14 прерываний, соответствующих сигналу Reset (Сброс), немаскируемому прерыванию (NMI - None Masked Interrupt) и прерываниям с номерами 4 -15.

С62хх содержат внутрикристальную память, которая может использоваться как память программ или кэш-память. Интерфейс внешней памяти процессора объединяет в единое адресное пространство внутреннюю и внешнюю память.

Внутрикристальная память разделена на память данных и память программ. Процессоры семейства С62хх имеют два 32-разрядных порта к памяти данных и один 256-разрядный порт к памяти программ для выборки инструкций. Процессор TMS320C6201 содержит на кристалле по 64 Кбайт памяти данных и программ. В процессоре используется расслоение памяти данных (четыре 16-разрядных банка) для повышения скорости выборки за счет одновременного обращения к различным банкам памяти.

Дополнительно процессоры семейства С62хх могут содержать на кристалле интерфейс внешней памяти, контроллер ПДП, интерфейс хост-порта (HPI), средства энергосбережения, расширенные буферизированные последовательные порты, 32-разрядные таймеры.

Следующий представитель семейства TMS320C6x - микропроцессор TMS320C6701 поддерживает операции с плавающей точкой, имеет более широкий (128 бит) интерфейс внешней памяти и меньшую частоту работы - 167 МГц.

В состав микропроцессора TMS320C6701 включены дополнительные функциональные модули:

- М-модуль умножения 24 32-разрядных целочисленных данных и 32 64-разрядных данных в формате с плавающей точкой;

- L-модуль выполнения арифметических операций над 32 40-разрядными целочисленными данными и 32 64-разрядными данными в формате с плавающей точкой;

- S-модуль выполняет операции сдвига, перехода и отдельные операции с 32 64-разрядными данными в формате с плавающей точкой;

- D-модуль, выполняющий адресные операции.

Пиковая производительность данного микропроцессора составляет 688 Mflops.